Catalog excerpts

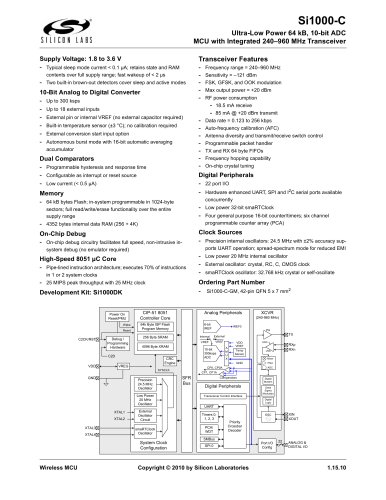

Wireless MCU Copyright © 2010 by Silicon Laboratories 1.15.10 CIP-51 8051 Controller Core 64k Byte ISP Flash Program Memory 256 Byte SRAM SFR Bus 4096 Byte XRAM VDD XTAL1 SYSCLK System Clock Configuration External Oscillator Circuit Precision 24.5 MHz Oscillator Debug / Programming Hardware Power On Reset/PMU Reset C2D C2CK/RST Wake XTAL2 Low Power 20 MHz Oscillator smaRTClock Oscillator XTAL3 XTAL4 GND VREG CRC Engine RXp RXn TX XIN XOUT Analog Peripherals Comparators + - 10-bit 300ksps ADC AMUX Temp Sensor External VREF Internal VREF VDD 6-bit IREF VREF GND IREF0 CP0, CP0A + - CP1, CP1A XCVR (240-960 MHz) OSC PA LNA AGC Digital Modem Delta Sigma Modulator Digital Logic Mixer PGA ADC Port I/O Config Digital Peripherals UART Timers 0, 1, 2, 3 PCA/ WDT SMBus Priority Crossbar Decoder Transceiver Control Interface SPI 0 22 ANALOG & DIGITAL I/O Si1000-C Ultra-Low Power 64 kB, 10-bit ADC MCU with Integrated 240–960 MHz Transceiver Supply Voltage: 1.8 to 3.6 V -Typical sleep mode current < 0.1 ìA; retains state and RAM contents over full supply range; fast wakeup of < 2 ìs -Two built-in brown-out detectors cover sleep and active modes 10-Bit Analog to Digital Converter -Up to 300 ksps -Up to 18 external inputs -External pin or internal VREF (no external capacitor required) -Built-in temperature sensor (±3 °C); no calibration required -External conversion start input option -Autonomous burst mode with 16-bit automatic averaging accumulator Dual Comparators -Programmable hysteresis and response time -Configurable as interrupt or reset source -Low current (< 0.5 ìA) Memory -64 kB bytes Flash; in-system programmable in 1024-byte sectors; full read/write/erase functionality over the entire supply range -4352 bytes internal data RAM (256 + 4K) On-Chip Debug -On-chip debug circuitry facilitates full speed, non-intrusive in-system debug (no emulator required) High-Speed 8051 ìC Core -Pipe-lined instruction architecture; executes 70% of instructions in 1 or 2 system clocks -25 MIPS peak throughput with 25 MHz clock Development Kit: Si1000DK Transceiver Features - Frequency range = 240–960 MHz - Sensitivity = –121 dBm - FSK, GFSK, and OOK modulation - Max output power = +20 dBm - RF power consumption - 18.5 mA receive - 85 mA @ +20 dBm transmit - Data rate = 0.123 to 256 kbps - Auto-frequency calibration (AFC) - Antenna diversity and transmit/receive switch control - Programmable packet handler - TX and RX 64 byte FIFOs - Frequency hopping capability - On-chip crystal tuning Digital Peripherals -22 port I/O -Hardware enhanced UART, SPI and I2C serial ports available concurrently -Low power 32-bit smaRTClock -Four general purpose 16-bit counter/timers; six channel programmable counter array (PCA) Clock Sources -Precision internal oscillators: 24.5 MHz with ±2% accuracy supports UART operation; spread-spectrum mode for reduced EMI -Low power 20 MHz internal oscillator -External oscillator: crystal, RC, C, CMOS clock -smaRTClock oscillator: 32.768 kHz crystal or self-oscillate Ordering Part Number - Si1000-C-GM, 42-pin QFN 5 x 7 mm2

Open the catalog to page 1All Silicon Laboratories catalogs and technical brochures

-

ISOmodem Solutions Guide

2 Pages

-

PRODUCT SELECTOR GUIDE 2013

36 Pages

-

MCU Selector Guide

20 Pages

-

Wireless and RF Selector Guide

12 Pages

-

Human Interface Solutions Guide

12 Pages

-

Isolation Selector Guide

10 Pages

-

Microcontroller Selector Guide

20 Pages

-

Audio Applications Guide

24 Pages

-

USB Bridge Solutions

2 Pages

-

Si4032/31/30 ISM Transmitter

2 Pages

Archived catalogs

-

Broadcast Audio Solutions

2 Pages

-

Digital Power Solutions

2 Pages

-

Low-Voltage/Low-Power MCUs

2 Pages