Catalog excerpts

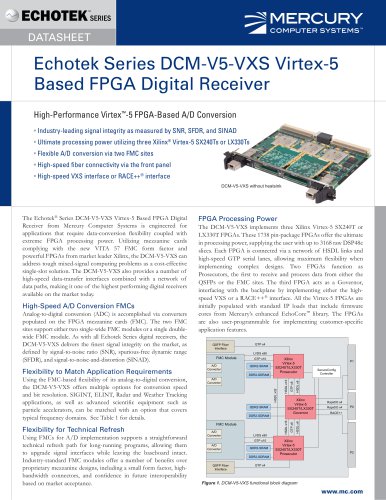

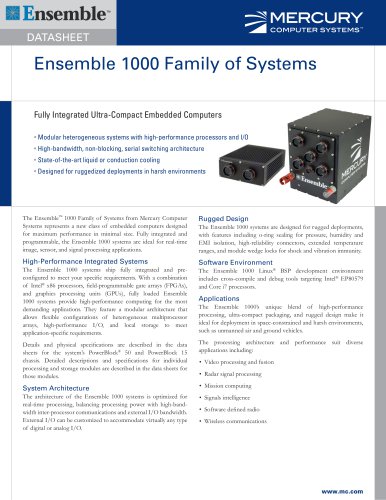

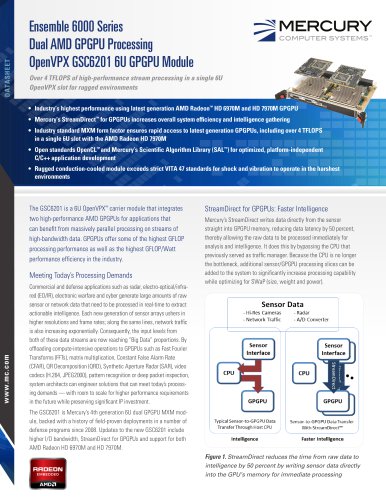

Echotek Series DCM-V5-VXS Virtex-5 Based FPGA Digital Receiver High-Performance Virtex™-5 FPGA-Based A/D Conversion • Industry-leading signal integrity as measured by SNR, SFDR, and SINAD • Ultimate processing power utilizing three Xilinx® Virtex-5 SX240Ts or LX330Ts • Flexible A/D conversion via two FMC sites • High-speed ber connectivity via the front panel • High-speed VXS interface or RACE++® interface DCM-V5-VXS without heatsink Flexibility for Technical Refresh Using FMCs for A/D implementation supports a straightforward technical refresh path for long-running programs, allowing them to upgrade signal interfaces while leaving the baseboard intact. Industry-standard FMC modules offer a number of benets over proprietary mezzanine designs, including a small form factor, highbandwidth connectors, and condence in future interoperability based on market acceptance. QSFP Fiber Interface Using the FMC-based exibility of its analog-to-digital conversion, the DCM-V5-VXS offers multiple options for conversion speed and bit resolution. SIGINT, ELINT, Radar and Weather Tracking applications, as well as advanced scientic equipment such as particle accelerators, can be matched with an option that covers typical frequency domains. See Table 1 for details. Flexibility to Match Application Requirements QSFP Fiber Interface Analog-to-digital conversion (ADC) is accomplished via converters populated on the FPGA mezzanine cards (FMC). The two FMC sites support either two single-wide FMC modules or a single doublewide FMC module. As with all Echotek Series digital receivers, the DCM-V5-VXS delivers the nest signal integrity on the market, as dened by signal-to-noise ratio (SNR), spurious-free dynamic range (SFDR), and signal-to-noise-and-distortion (SINAD). The DCM-V5-VXS implements three Xilinx Virtex-5 SX240T or LX330T FPGAs. These 1738 pin-package FPGAs offer the ultimate in processing power, supplying the user with up to 3168 raw DSP48e slices. Each FPGA is connected via a network of HSDL links and high-speed GTP serial lanes, allowing maximum exibility when implementing complex designs. Two FPGAs function as Prosecutors, the rst to receive and process data from either the QSFPs or the FMC sites. The third FPGA acts as a Governor, interfacing with the backplane by implementing either the highspeed VXS or a RACE++® interface. All the Virtex-5 FPGAs are initially populated with standard IP loads that include rmware cores from Mercury’s enhanced EchoCore™ library. The FPGAs are also user-programmable for implementing customer-specic application features. High-Speed A/D Conversion FMCs FPGA Processing Power The Echotek® Series DCM-V5-VXS Virtex-5 Based FPGA Digital Receiver from Mercury Computer Systems is engineered for applications that require data-conversion exibility coupled with extreme FPGA processing power. Utilizing mezzanine cards complying with the new VITA 57 FMC form factor and powerful FPGAs from market leader Xilinx, the DCM-V5-VXS can address tough mixed-signal computing problems as a cost-effective single-slot solution. The DCM-V5-VXS also provides a number of high-speed data-transfer interfaces combined with a network of data paths, making it one of the highest performing digital receivers available on the market today. Figure 1. DCM-V5-VXS functional block diagram

Open the catalog to page 1

Table 1. A/D Conversion Options Channels, Speed, and Resolution Option Model* Consult factory Consult factory Consult factory Consult factory *All options are available in a VME version with no P0 connector. FPGA Connectivity The DCM-V5-VXS FPGA connectivity consists of a network of HSDL links and GTP serial lanes between the FPGAs and various interfaces, allowing for maximum exibility when moving data. Each of the two Prosecutor FPGAs is connected to its respective FMC site via 80 LVDS pairs and 10 GTP serial lanes. An additional four GTP serial lanes connect them to their QSFP interface....

Open the catalog to page 2

Software Mercury provides driver applications for the DCM-V5-VXS supported by the following operating systems: • Timesys® Linux for VPA-200 • VxWorks® 5.5 Environmental The DCM-V5-VXS is designed to meet Mercury VH ruggedization. The board has also been developed under a conduction-cooled envelope for applications that require additional ruggedization characteristics. Contact the factory for availability of conduction-cooled modules. Specications FPGAs 2 Prosecutor FPGAs Xilinx Virtex-5 SX240T or Xilinx Virtex-5 LX330T 1 Governor FPGA Xilinx Virtex-5 SX240T or Xilinx Virtex-5 LX330T Memory...

Open the catalog to page 3

Challenges Drive Innovation, Echotek, and RACE++ are registered trademarks, and EchoCore is a trademark of Mercury Computer Systems, Inc. RapidIO is a registered trademark of the RapidIO Trade Association. Other products mentioned may be trademarks or registered trademarks of their respective holders. Mercury Computer Systems, Inc. believes this information is accurate as of its publication date and is not responsible for any inadvertent errors. The information contained herein is subject to change without notice. Copyright © 2010 Mercury Computer Systems, Inc. Europe Mercury Computer...

Open the catalog to page 4All MERCURY SYSTEMS catalogs and technical brochures

-

MFCC-8557

3 Pages

-

MFCC-8556

2 Pages

-

MFCC-8558

3 Pages

-

ROCK-2

4 Pages

-

CIO5-2040

2 Pages

-

DCM-V5-XMC Digital Receiver

2 Pages

-

PowerBlock 50

2 Pages