Website:

Delta Tau

Website:

Delta Tau

Catalog excerpts

Turbo PMAC Application Notes Turbo PMAC controllers can be provided with several different CPU and memory configurations. The user specifies the desired configuration by ordering one of the Opt 5xx CPU options. The x immediately following the 5 is a letter specifying the processor type, each with different speed and internal memory capacity. The second x is a number specifying the amount of memory external to the processor. Processor Types Turbo PMAC controllers use digital signal processors (DSPs) from Freescale (formerly Motorola) of the DSP563xx family. > The Freescale (formerly Motorola) DSP563xx CPUs used in Turbo PMAC controllers utilize a Harvard architecture, with separate memory banks for data and instructions. This architecture is more efficient, but less flexible, than the more common von Neumann architecture used in most general-purpose computers. In a given application, a given bank of physical memory cannot be switched between the two uses. Each CPU/memory configuration of the Turbo PMAC makes a specific division between the two banks of memory, and this division cannot be changed by the user. > The instruction memory bank contains the actual machine-code instructions executed by the processor. These instructions must have been compiled or assembled from the source code before loading into the Turbo PMAC memory. This bank is called the P (program) memory bank, and is very seldom accessed directly by a user. Each instruction register is a 24-bit word. There are four possible sets of instructions in the P memory bank: 1. Firmware: This code is written and loaded by Delta Tau, and must be present for the Turbo PMAC to operate.2. Compiled PLCs: The user can load up to 32 compiled PLC programs into Turbo PMACs P memory. The download routines of the Executive program and PCOMM library automatically compile code designated for compiled PLCs and load it into the appropriate section of Turbo PMAC P memory. 3. User-Written Servo: The user can load a custom servo algorithm either an Open Servo algorithm compiled with the Pro Executive program, or assembled with a cross-assembler provided by Freescale/Motorola. 4. User-Written Phase: The user can load a custom phase (commutation) algorithm, assembled with a cross-assembler provided by Freescale/Motorola. > The data memory bank contains the data registers on which the instructions act. Note that interpreted programs Җ both motion programs and uncompiled PLC programs are data, because they do not contain the actual machine-code instructions that the processor directly executes. The data memory bank is organized as a set of 48-bit double words, each split into an X register and a Y register. In addition to the user֒s interpreted programs, the data memory bank contains fixed-use registers, and any defined data buffers that the user creates, such as compensation tables, lookahead buffers, and data- gathering buffers. > Turbo PMAC Memory Configurations 1 size="-1">

Open the catalog to page 1

Turbo PMAC Application Notes >

Open the catalog to page 2

Turbo PMAC Application Notes >

Open the catalog to page 3All Delta Tau catalogs and technical brochures

-

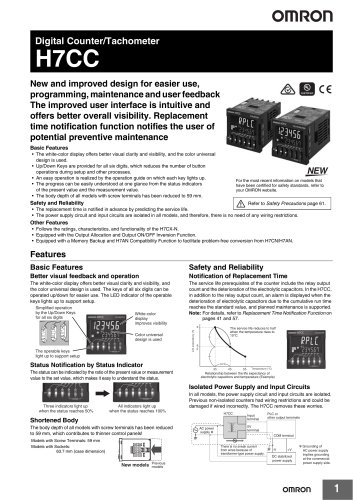

Digital Counter/Tachometer H7CC

64 Pages

-

TURBO PMAC2 VME ULTRALITE

7 Pages

-

TURBO PMAC2 REALTIME EXPRESS

3 Pages

-

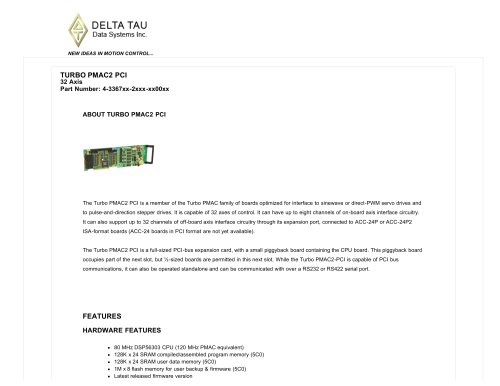

TURBO PMAC2 PCI

7 Pages

-

TURBO PMAC VME

6 Pages

-

POWER UMAC CPU 256 Axis

4 Pages

-

3U042

4 Pages

-

3U081

4 Pages

-

3U151

4 Pages

-

ACC-8D OPT4

3 Pages

-

ACC-8D OPT4A

3 Pages

-

ADVANTAGE 900 BASIC PACKAGE

3 Pages

-

PMAC MINI PCI 8 Axis

7 Pages

-

PMAC PCI 8 Axis

7 Pages

-

PMAC PCI LITE 8 Axis

7 Pages

-

PMAC VME 8 Axis

6 Pages

-

PMAC2A PC/104

6 Pages

-

POWER UMAC

4 Pages

-

TURBO UMAC

6 Pages

-

PMAC-NC PRO2 RUNTIME

3 Pages

-

Turbo Clipper Drive

2 Pages

-

Battery Issues with PMAC ISA

5 Pages

-

Digital IO accessories

2 Pages

-

MLDT Sensor

1 Pages

-

Slow communications

1 Pages