Catalog excerpts

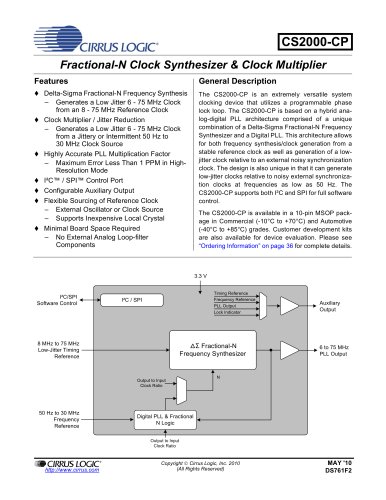

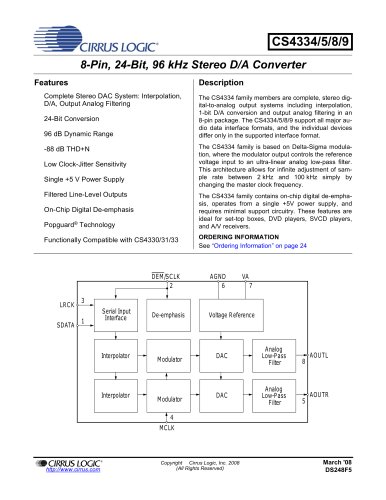

CS43198 130-dB, 32-Bit High-Performance DAC with Pseudodifferential Outputs System Features Applications • Smart phones, tablets, portable media players, laptops, digital headphones, powered speakers, AVR, home theater systems, Blu-ray/DVD/SACD players, and pro audio TSO Interrupt Sources XSP/DSD Audio Interface AOUTB REFB FLYC_VCP FLYP_VCP FLYN_VCP VCP_FILT+ VCP_FILTFLYP_VA FLYN_VA -VA Interpolation Filter and Volume Control Register/Hardware Configuration DSD Processor Popguard® Circuitry Control Port Level Translator Copyright Cirrus Logic, Inc. 2015–2017 (All Rights Reserved) Charge Pump Internal Voltage Reference Interpolation Filter and Volume Control Analog Supply (VA,VCP) Battery Supply +1.8V (VP) FILT+ FILT- Digital LDOs Digital Core Internal Interface Supply (VL) Supply (VD) +1.8V +1.8V Level Translator • Direct Stream Digital (DSD®) path — Up to 256•Fs DSD Enhanced oversampling DAC architecture — Patented DSD processor — 32-bit resolution – On-chip 50-kHz filter to meet Scarlet Book Super — Up to 384-kHz sampling rate Audio Compact Disk (SACD) recommendations — Low clock jitter sensitivity – Matched PCM and DSD analog output levels — Auto mute detection – Nondecimating volume control with 0.5-dB step size Integrated high performance outputs and soft ramp — 130-dB dynamic range (A-weighted) – DSD and Pulse-code modulation (PCM) mixing for — –115-dB total harmonic distortion + noise (THD+N) alerts — 110-dB interchannel isolation — Dedicated DSD and DoP pin interface — Up to 2-Vrms pseudodifferential stereo analog output • Direct DSD path support Headphone detection • Serial audio input path — Headphone plug-in detection — Programmable Hi-Fi digital filter — Popguard® technology eliminates pop noise — Five selectable digital filter responses Integrated PLL – Low-latency Mode minimizes pre-echo — Support for 11.2896-/22.5792-, 12.288-/24.576-, 9.6-/ – 110 dB of stopband attenuation 19.2-, 12-/24-, and 13-/26-MHz system MCLK rates — Supports sample rates from 32 to 384 kHz — Reference clock sourced from XTI/MCLK pin — I2S, right-justified, left-justified, TDM, and — System clock output DSD-over-PCM (DoP) interface Mono Mode (differential) support — Master or slave operation I2C control—up to 1 MHz — Volume control with 0.5-dB step size and soft ramp — 44.1 kHz deemphasis and inverting feat

Open the catalog to page 1

CS43198 General Description The CS43198 is a high-performance, 32-bit resolution, stereo audio DAC that supports up to 384-kHz sampling frequency with pseudodifferential analog outputs. The advanced 32-bit oversampled multibit modulator with mismatch shaping technology eliminates distortion due to on-chip component mismatch. Proprietary digital-interpolation filters support five selectable filter responses with pseudo-linear phase and ultralow latency to minimize pre-echos and ringing artifacts. An on-chip programmable filter is available for further response customization. Other features...

Open the catalog to page 2

CS43198 Table of Contents 1 Pin Assignments and Descriptions . . . . . . . . . . . . . . . . . . . . . . 4 1.1 40-Pin QFN (Top-Down, Through-Package View) . . . . . . . . . 4 1.2 42-Ball WLCSP (Top-down, Through-Package View) . . . . . . 5 1.3 Pin Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 1.4 Electrostatic Discharge (ESD) Protection Circuitry . . . . . . . . 8 2 Typical Connection Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 10 3 Characteristics and Specifications . . . . . . . . . . . . . . . . . . . . . 12 Table 3-1. Parameter...

Open the catalog to page 3

CIRRUS LOGIC CS43198 1 Pin Assignments and Descriptions 1 Pin Assignments and Descriptions 1.1 40-Pin QFN (Top-Down, Through-Package View) Q w < Q W Q RESET TNT VP VCP FLYP_VCP FLYC_VCP HP_DETECT VCP FILT+ Figure 1-1. Top-Down (Through-Package) View—QFN 40-Pin Diagram

Open the catalog to page 4

1.2 42-Ball WLCSP (Top-down, Through-Package View) 1.2 42-Ball WLCSP (Top-down, Through-Package View) Charge Pump Power Supplies Figure 1-2. Top-Down (Through-Package) View—42-Ball WLCSP Package

Open the catalog to page 5

I.The power supply is determined by ADPT_PWR setting (see Section 4.3.1). VP is used if ADPT_PWR = 001 (VP_LDO Mode) or when necessary for ADPTPWR = 111 (Adapt-to-Signal Mode).

Open the catalog to page 7

1.4 Electrostatic Discharge (ESD) Protection Circuitry 1.4 Electrostatic Discharge (ESD) Protection Circuitry ESD-sensitive device. The CS43198 is manufactured on a CMOS process. Therefore, it is generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken while handling and storing this device. This device is qualified to current JEDEC ESD standards. Fig. 1-3 provides a composite view of the ESD domains showing the ESD protection paths between each pad and the substrate (GND), as well as the interrelations between some domains. Note that this...

Open the catalog to page 8

1.4 Electrostatic Discharge (ESD) Protection Circuitry Table 1-2. ESD Domains (Cont.) ESD Domain VA/–VA Signal Name (See * in Topology Figures for Pad) FLYN_VA FLYP_VA FILT+ FILT– RESET INT VP/VCP_FILT– FLYP_VCP FLYC_VCP HP_DETECT VCP_FILT+/ FLYN_VCP VCP_FILT– AOUTA AOUTB REFA REFB VP/GNDCP Domain VCP_FILT+/VCP_FILT– Domain VP/VCP_FILT– Domain

Open the catalog to page 9

2 Typical Connection Diagram 2 Typical Connection Diagram VL DoP / DSD Digital Audio Source PCM / DoP Digital Audio Source Audio Devices OUTB AOUTA Applications Processor / MicroController Analog Signal Conditioning All external passive component values shown are nominal . Clocking Configuration XTAL External MCLK System Clock REFB RESET Headphone Connector Key for Capacitor Types Required : * Use low ESR, X7R/X5R capacitors If no type symbol is shown next to a capacitor, any type may be used. ** Use C0G capacitors. XTI/MCLK XTI/MCLK VCP_FILT Configuration EXT_VCPFILT = 0 VCP VCP_FILT+...

Open the catalog to page 10

2 Typical Connection Diagram VL Audio Devices FILTXTI / MCLK DoP / DSD Digital Audio Source PCM / DoP Digital Audio Source Applications Processor / MicroController GNDA HP_DETECT All external passive component values shown are nominal. Clocking Configuration XTAL External MCLK System Clock Analog Signal Conditioning Key for Capacitor Types Required: * Use low ESR, X7R/X5R capacitors If no type symbol is shown next to a capacitor, any type may be used. ** Use C0G capacitors. XTI/MCLK XTI/MCLK VCP_FILT Configuration EXT_VCPFILT = 0 VCP VCP_FILT+ VCP_FILT– GNDCP VCP VCP_FILT+ VCP_FILT– GNDCP...

Open the catalog to page 11All Cirrus Logic catalogs and technical brochures

-

Professional Service Partners

12 Pages

-

CS5343/44

21 Pages

-

WM0011

233 Pages

-

CS4970x4

31 Pages

-

CS4953xx

37 Pages

-

WM9081

103 Pages

-

CS42L51

84 Pages

-

CS42L42

184 Pages

-

CS43131

156 Pages

-

CS43130

137 Pages

-

CS5351

23 Pages

-

CS5346

38 Pages

-

CS5341/42

21 Pages

-

CS35L32

51 Pages

-

CS35L00/01/03

34 Pages

-

Energy Measurement Brochure

13 Pages

Archived catalogs

-

CS48DV2/6

2 Pages

-

Mixed-Signal Audio Brochure

64 Pages