Catalog excerpts

Clock and Timing ICs for Wireline Applications In Networks and Beyond Analog Devices, Inc. (ADI), is a global leader in high performance semiconductors for signal processing applications and a leader in integrated circuits for the telecommunications market. ADI offers a wide portfolio to address the needs of integrated clock solutions targeted at critical timing functions. By combining world leadership in data converters and years of expertise in frequency/phase synthesis techniques, ADI’s clock generation, synchronization, and distribution ICs offer industry-leading performance and enhanced value to our customers. • Flexible, integrated designs with critical clocking functions • Innovative clock ICs that can be used in wired and wireless networks, providing cost efficient solutions for high performance clock generation and distribution • Wide range of integrated clock products that provide designers with the flexibility needed to satisfy the most demanding clocking requirements www.analog.com/clocks

Open the catalog to page 1

Distribution and Synchronization Analog Devices leverages its leadership position in high performance wireless clocking applications to provide leading-edge solutions for the wired market. Performance and features found in our network clock products provide high reliability, flexibility, and ease of design to build a cutting edge solution for the next generation of network standards. Phase synchronization occurs when the phases at the output and at the input are related with a fixed relative phase angle. The most common phase synchronization is when the edge of the output is aligned with...

Open the catalog to page 2

TIMING/SYNCHRONIZATION CARDS E R AV SL LINE CARDS TE AS M N N CK O IO O ATI AT N CL ER NIZ TIO N O LA GECHRNS A YN TR S N IO AT IZ N G RO IN CE CH TIM UR N SO SY N CK TIO LOIBU C R T IS N CK TIO LOIBU C R T IS D D REF_P REF_S REF_P REF_S BACKPLANE ADI CLOCKS ARE USED ON TIMING/SYNCHRONIZATION CARDS AND LINE CARDS. LINE CARD BACKPLANE FRAMER SERIALIZER CLOCK GENERATION, SYNCHRONIZATION, AND TRANSLATION FRAMER LDD CLOCK DISTRIBUTION DESERIALIZER LASER DIODE TX TO SONET/SDH/PDH NETWORK OPTICAL MODULE CDR POST AMP TIA PHOTO DIODE RX ADI CLOCKING SOLUTIONS TRANSLATE FREQUENCIES AND CLEAN UP...

Open the catalog to page 3

Network Clock Product Highlights The AD9557/AD9558 (the most recent additions to ADI's network clock family) provide jitter cleanup with jitter generation of <0.4 ps rms. They support all major network frequency translations (2 kHz to 1.25 GHz input and 360 kHz to 1.25 GHz output) including those using FEC. The user can fully program either device via its SPI port or select from a group of predefined configurations via pin strapping. The performance and versatility of the AD9557/AD9558 provide a cost competitive solution to traditional PLLs that rely on expensive voltage controlled crystal...

Open the catalog to page 4

The architecture of the AD9548 all-digital PLL offers unparalleled flexibility and high performance with virtually no part-to-part variation. The device internally samples the time difference between the feedback and reference clock edges. The time samples pass through a digital loop filter that relies on programmable numeric coefficients to establish the loop bandwidth of the digital PLL (from 0.001 Hz to 100 kHz). The numeric output of the digital loop filter is a sequence of frequency tuning words that drives a 48-bit direct digital synthesizer (DDS), which provides frequency resolution...

Open the catalog to page 5

Oscillators are used in a wide variety of applications but can be expensive, especially at high frequencies and for applications requiring temperature stability. They also tend to be among the least reliable components in a system. Furthermore, oscillators that provide nonstandard frequencies usually come at a premium and typically have long lead times. Few alternatives exist for generating nonstandard clock frequencies with low noise and high The AD9552 fractional-N PLL is one alternative that supports frequency translations of up to 800 MHz with very fine tuning resolution and allows...

Open the catalog to page 6

Each PLL provides two differential output drivers with each driver configurable as a pair of single-ended CMOS outputs. Furthermore, a dedicated CMOS output provides a buffered copy of the input reference clock. The AD9577 reference clock input operates from 19.44 MHz to 27 MHz and supports either a single-ended CMOS driver or direct connection of a crystal resonator. The AD9577 is fuse programmable, making it an attractive candidate for high volume applications. The AD9577 complements the AD9557/AD9558 in line card designs requiring clock cleanup and frequency plans for both SONET/SDH and...

Open the catalog to page 7

| 8 Clock and Timing ICs for Wireline Applications 0.008 to 200 0.008 to 200 SPI or pin Pin AD9549 AD9550 None Hitless and build out Hitless 0.3 to 400 0.008 to 250 None I2C or preset SPI AD9577 AD9959 None 1 to 500 19 to 26 25 Phase build out None 25 Phase build out 1 2 <1 to 200 13 to 650 Multiple fixed (including 106.25 MHz, 156.25 MHz, 33.33 MHz, 100 MHz, and 125 MHz) Multiple fixed (including 100 MHz, 125 MHz, 155.25 MHz, 159.375 MHz, 161.13 MHz, and 312.5 MHz) None None None None 0.1 Hz/2 kHz 0.002 to 1250 1 1 Comparator dependent 1 1 2/4 2 2 2 2 21/41 21/41 2 0.4 ps integer/ 0.9 ps...

Open the catalog to page 8

ADI's Clock Portfolio—More Than Just Wired Networks The highly integrated dual PLL architecture of the AD9523 provides a jitter cleaner with 14 channels of clock generation and distribution to meet all the needs of a wireless base station transceiver (the AD9524 is a six output version). The PLL1 relies on an external VCXO to provide jitter cleanup of the remote radio unit reference clock. PLL2 has an integrated VCO that translates the low jitter output of PLL1 to -3.7 GHz. The output buffer stage adds less than 200 fs (femtoseconds) rms jitter. These integrated blocks enable a complete...

Open the catalog to page 9

Support Tools and Design Assistance ADIsimCLK Clock Circuit Design and Simulation Tool ADIsimCLK™ is the design tool developed specifically for Analog Devices’ range of ultralow jitter clock distribution and clock generation products. The ADIsimCLK tool enables designers to observe detailed performance data for a simulated clock distribution design within minutes. Optimization of the clock circuit can be accomplished in this interactive environment with spreadsheet-like simplicity and interactivity. For a free download of the complete software package, please visit www.analog.com/ADIsimCLK....

Open the catalog to page 10All Analog Devices catalogs and technical brochures

-

HMC722LP3E

8 Pages

-

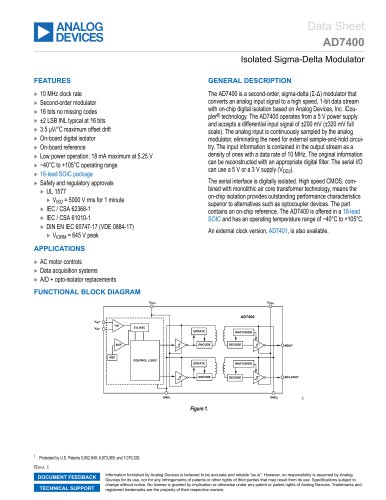

Isolated Sigma-Delta Modulator

17 Pages

-

HMC853 Data Sheet

10 Pages

-

AN-1084

8 Pages

-

AN-1091

2 Pages

-

AN_737

8 Pages

-

AN-0982

4 Pages

-

ADF7024

24 Pages

-

AD9915

48 Pages

-

AD9914

48 Pages

-

ADRF6612

59 Pages

-

ADRF6820

48 Pages

-

ADL5246

32 Pages

-

ADA4961

22 Pages

-

AN-1141

8 Pages

-

AN-698

36 Pages

-

Temperature Sensors

2 Pages

-

Reference Circuits

8 Pages

-

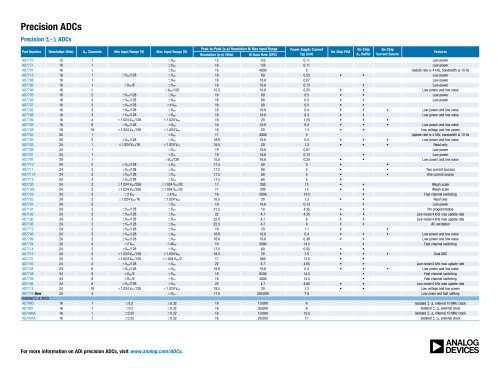

Precision ADCs

16 Pages

-

ADR02ACHIPS: ADR02ACHIPS

8 Pages

-

AD9364 RF Agile Transceiver

32 Pages

-

Digital Temperature Sensors

2 Pages

-

Digital to Analog Converter ICs

12 Pages

-

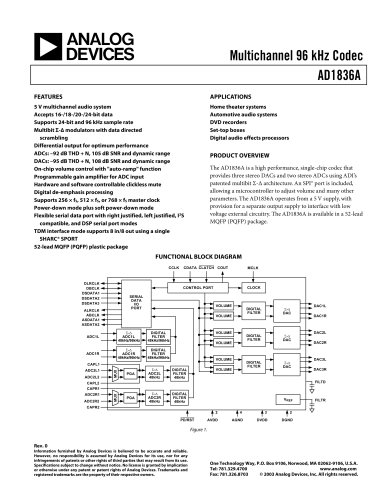

AD1836A: Multichannel 96 kHz Codec

24 Pages

Archived catalogs

-

Powering ADI Components

8 Pages

-

Zero-Drift Amplifiers

2 Pages