ADSP-BF512/ADSP-BF514/ADSP-BF514F16/ADSP-BF516/ADSP-BF518/ADSP-BF518F16 Blackfin Embedded Processor

1 /

68Pages

Catalog excerpts

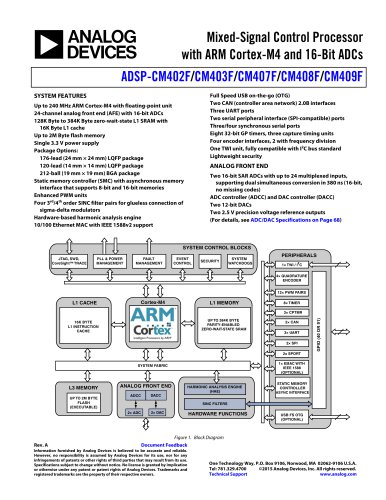

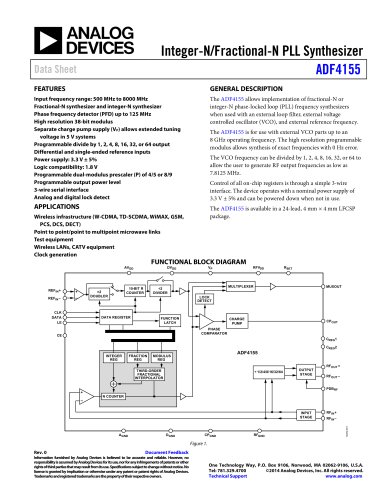

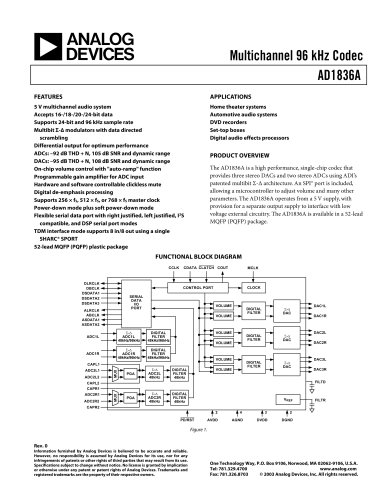

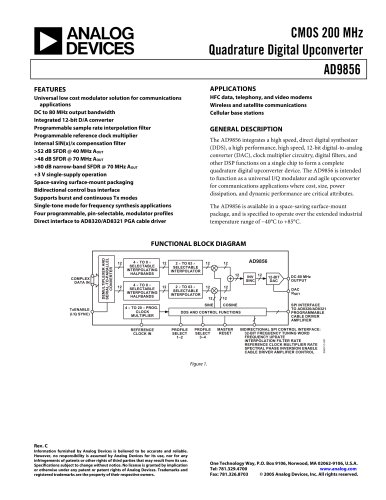

Blackfin Embedded Processor ADSP-BF512/BF514/BF514F16/BF516/BF518/BF518F16 FEATURES Up to 400 MHz high performance Blackfin processor Two 16-bit MACs, two 40-bit ALUs, four 8-bit video ALUs, 40-bit shifter RISC-like register and instruction model for ease of programming and compiler-friendly support Advanced debug, trace, and performance monitoring Wide range of operating voltages. See Operating Conditions on Page 22 Qualified for Automotive Applications. See Automotive Products on Page 67 168-ball CSP_BGA or 176-lead LQFP_EP (with exposed pad) IEEE 802.3-compliant 10/100 Ethernet MAC with IEEE 1588 support (ADSP-BF518/ADSP-BF518F16 only) Parallel peripheral interface (PPI), supporting ITU-R 656 video data formats 2 dual-channel, full-duplex synchronous serial ports (SPORTs), supporting 8 stereo I2S channels 12 peripheral DMAs, 2 mastered by the Ethernet MAC 2 memory-to-memory DMAs with external request lines Event handler with 56 interrupt inputs 2 serial peripheral interfaces (SPI) Removable storage interface (RSI) controller for MMC, SD, SDIO, and CE-ATA 2 UARTs with IrDA support 2-wire interface (TWI) controller Eight 32-bit timers/counters with PWM support 3-phase 16-bit center-based PWM unit 32-bit general-purpose counter Real-time clock (RTC) and watchdog timer 32-bit core timer 40 general-purpose I/Os (GPIOs) Debug/JTAG interface On-chip PLL capable of frequency multiplication MEMORY 116K bytes of on-chip memory External memory controller with glueless support for SDRAM and asynchronous 8-bit and 16-bit memories Optional 16M bit SPI flash with boot option Flexible booting options from internal SPI flash, OTP memory, external SPI/parallel memories, or from SPI/UART host devices Code security with Lockbox secure technology One-time-programmable (OTP) memory Memory management unit providing memory protection WATCHDOG TIMER PERIPHERAL ACCESS BUS COUNTER JTAG TEST AND EMULATION INTERRUPT CONTROLLER EXTERNAL PORT FLASH, SDRAM CONTROL Figure 1. Functional Block Diagram Blackfin and the Blackfin logo are registered trademarks of Analog Devices, Inc. Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A. Tel: 781.329.4700 ©2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

Open the catalog to page 1

ADSP-BF512/BF514/BF514F16/BF516/BF518/BF518F16 GENERAL DESCRIPTION The ADSP-BF512/ADSP-BF514/ADSP-BF514F16/ADSPBF516/ADSP-BF518/ADSP-BF518F16 processors are members of the Blackfin® family of products, incorporating the Analog Devices/Intel Micro Signal Architecture (MSA). Blackfin processors combine a dual-MAC state-of-the-art signal processing engine, the advantages of a clean, orthogonal RISC-like microprocessor instruction set, and single-instruction, multiple-data (SIMD) multimedia capabilities into a single instruction-set architecture. The processors are completely code compatible...

Open the catalog to page 3

ADSP-BF512/BF514/BF514F16/BF516/BF518/BF518F16 ADDRESS ARITHMETIC UNIT DECODE BARREL SHIFTER LOOP BUFFER CONTROL UNIT 32 DATA ARITHMETIC UNIT Figure 2. Blackfin Processor Core For certain instructions, two 16-bit ALU operations can be performed simultaneously on register pairs (a 16-bit high half and 16-bit low half of a compute register). If the second ALU is used, quad 16-bit operations are possible. The 40-bit shifter can perform shifts and rotates and is used to support normalization, field extract, and field deposit instructions. The program sequencer controls the flow of instruction...

Open the catalog to page 4

ADSP-BF512/BF514/BF514F16/BF516/BF518/BF518F16 The on-chip L1 memory system is the highest-performance memory available to the Blackfin processor. The off-chip memory system, accessed through the external bus interface unit (EBIU), provides expansion with SDRAM, flash memory, and SRAM, optionally accessing up to 132M bytes of physical memory. instruction can be issued in parallel with two 16-bit instructions, allowing the programmer to use many of the core resources in a single instruction cycle. The Blackfin processor assembly language uses an algebraic syntax for ease of coding and...

Open the catalog to page 5

ADSP-BF512/BF514/BF514F16/BF516/BF518/BF518F16 • Serial Interface Architecture—SPI compatible with Mode 0 and Mode 3 The processors internally connect to the flash memory die with the SPI0SCK, SPI0SEL4 or PH8, SPI0MOSI, and SPI0MISO signals similar to an external SPI flash (for signal descriptions, see Table 2). To further provide a secure processing environment, these internally connected signals are not exposed outside of the package. For this reason, programming the ADSP-BF51xF flash memory is performed by running code on the processor and cannot be programmed from external signals. Data...

Open the catalog to page 6

ADSP-BF512/BF514/BF514F16/BF516/BF518/BF518F16 Table 2. Internal Flash Memory Signal Descriptions Symbol Serial Clock Provides the timing of the serial interface. Commands, addresses, or input data are latched on the rising edge of the clock input, while output data is shifted out on the falling edge of the clock input. Serial Data Input Transfers commands, addresses, or data serially into the device. Inputs are latched on the rising edge of the serial clock. Serial Data Output Transfers data serially out of the device. Data is shifted out on the falling edge of the serial clock. Flash busy...

Open the catalog to page 7

ADSP-BF512/BF514/BF514F16/BF516/BF518/BF518F16 (EVT), and lists their priorities are described in the ADSP-BF51x Blackfin Processor Hardware Reference Manual “System Interrupts” chapter. System Interrupt Controller (SIC) The system interrupt controller provides the mapping and routing of events from the many peripheral interrupt sources to the prioritized general-purpose interrupt inputs of the CEC. Although the processors provide a default mapping, the user can alter the mappings and priorities of interrupt events by writing the appropriate values into the interrupt assignment registers...

Open the catalog to page 8All Analog Devices catalogs and technical brochures

-

HMC722LP3E

8 Pages

-

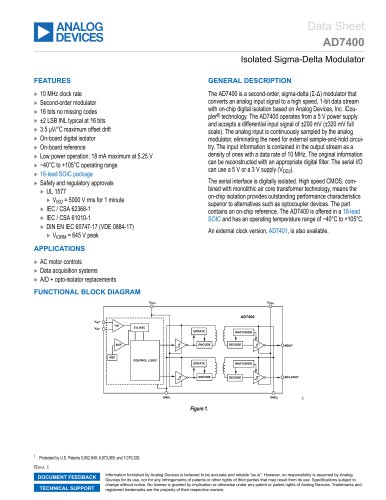

Isolated Sigma-Delta Modulator

17 Pages

-

HMC853 Data Sheet

10 Pages

-

AN-1084

8 Pages

-

AN-1091

2 Pages

-

AN_737

8 Pages

-

AN-0982

4 Pages

-

ADF7024

24 Pages

-

AD9915

48 Pages

-

AD9914

48 Pages

-

ADRF6612

59 Pages

-

ADRF6820

48 Pages

-

ADL5246

32 Pages

-

ADA4961

22 Pages

-

AN-1141

8 Pages

-

AN-698

36 Pages

-

Temperature Sensors

2 Pages

-

Reference Circuits

8 Pages

-

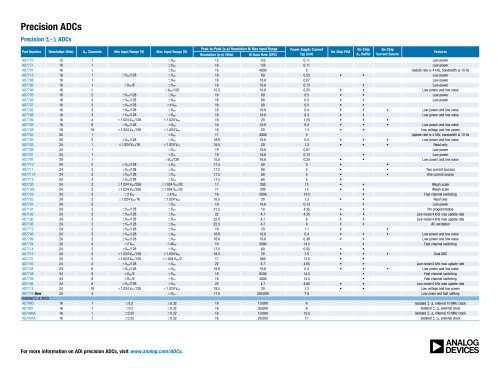

Precision ADCs

16 Pages

-

ADR02ACHIPS: ADR02ACHIPS

8 Pages

-

AD9364 RF Agile Transceiver

32 Pages

-

Digital Temperature Sensors

2 Pages

-

Digital to Analog Converter ICs

12 Pages

-

AD1836A: Multichannel 96 kHz Codec

24 Pages

Archived catalogs

-

Powering ADI Components

8 Pages

-

Zero-Drift Amplifiers

2 Pages