AD7262: 1 MSPS, 12-Bit, Simultaneous Sampling SAR ADC with PGA and Four Comparators Data Sheet

1 /

32Pages

Catalog excerpts

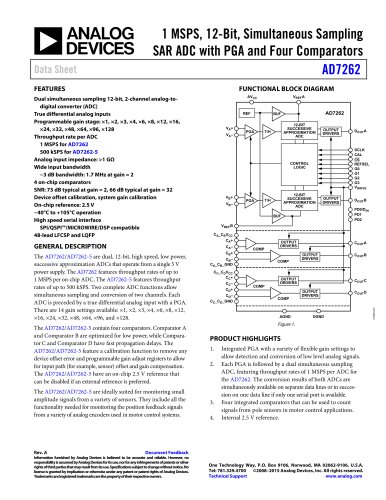

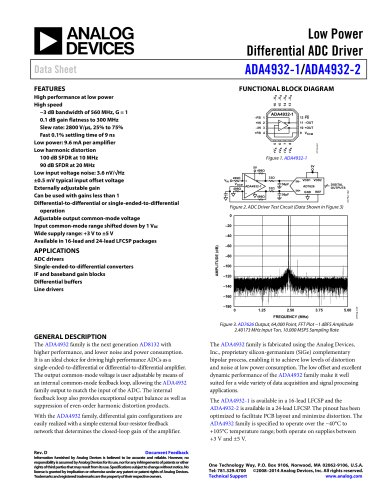

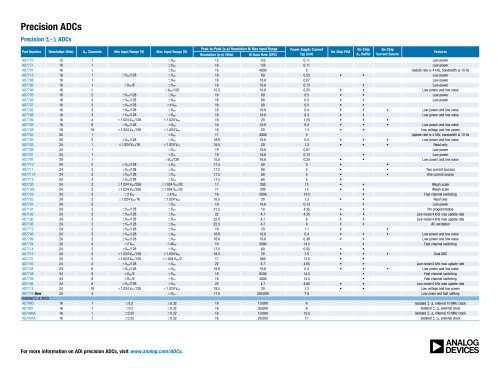

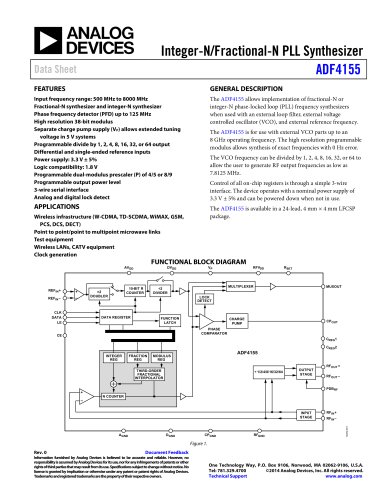

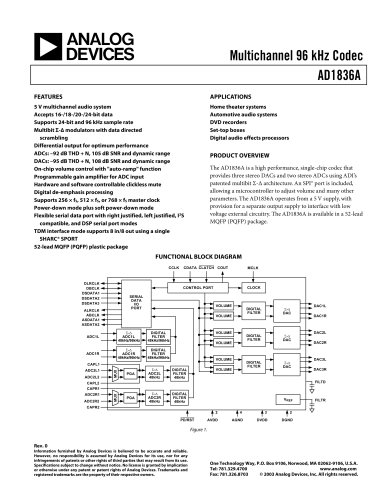

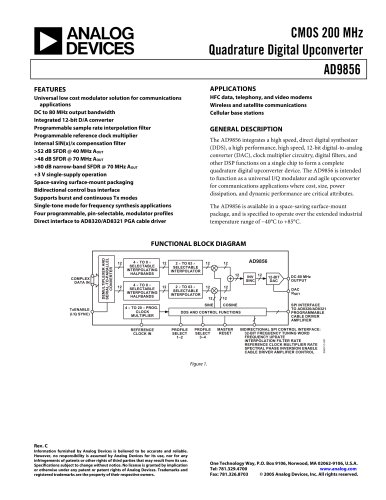

FUNCTIONAL BLOCK DIAGRAM Dual simultaneous sampling 12-bit, 2-channel analog-todigital converter (ADC) True differential analog inputs Programmable gain stage: ×1, ×2, ×3, ×4, ×6, ×8, ×12, ×16, ×24, ×32, ×48, ×64, ×96, ×128 Throughput rate per ADC 1 MSPS for AD7262 500 kSPS for AD7262-5 Analog input impedance: >1 GΩ Wide input bandwidth −3 dB bandwidth: 1.7 MHz at gain = 2 4 on-chip comparators SNR: 73 dB typical at gain = 2, 66 dB typical at gain = 32 Device offset calibration, system gain calibration On-chip reference: 2.5 V −40°C to +105°C operation High speed serial interface SPI/QSPI™/MICROWIRE/DSP compatible 48-lead LFCSP and LQFP OUTPUT DRIVERS The AD7262/AD7262-5 are ideally suited for monitoring small amplitude signals from a variety of sensors. They include all the functionality needed for monitoring the position feedback signals from a variety of analog encoders used in motor control systems. OUTPUT DRIVERS SCLK CAL CS REFSEL G0 G1 G2 G3 VDRIVE The AD7262/AD7262-5 contain four comparators. Comparator A and Comparator B are optimized for low power, while Comparator C and Comparator D have fast propagation delays. The AD7262/AD7262-5 feature a calibration function to remove any device offset error and programmable gain adjust registers to allow for input path (for example, sensor) offset and gain compensation. The AD7262/AD7262-5 have an on-chip 2.5 V reference that can be disabled if an external reference is preferred. CONTROL LOGIC GENERAL DESCRIPTION The AD7262/AD7262-5 are dual, 12-bit, high speed, low power, successive approximation ADCs that operate from a single 5 V power supply. The AD7262 features throughput rates of up to 1 MSPS per on-chip ADC. The AD7262-5 features throughput rates of up to 500 kSPS. Two complete ADC functions allow simultaneous sampling and conversion of two channels. Each ADC is preceded by a true differential analog input with a PGA. There are 14 gain settings available: ×1, ×2, ×3, ×4, ×6, ×8, ×12, ×16, ×24, ×32, ×48, ×64, ×96, and ×128. OUTPUT DRIVERS COUTA OUTPUT DRIVERS OUTPUT DRIVERS COUTC OUTPUT DRIVERS Integrated PGA with a variety of flexible gain settings to allow detection and conversion of low level analog signals. Each PGA is followed by a dual simultaneous sampling ADC, featuring throughput rates of 1 MSPS per ADC for the AD7262. The conversion results of both ADCs are simultaneously available on separate data lines or in succession on one data line if only one serial port is available. Four integrated comparators that can be used to count signals from pole sensors in motor control applications. Internal 2.5 V reference. Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2008–2015 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com Data Sheet 1 MSPS, 12-Bit, Simultaneous Sampling SAR ADC with PGA and Four Comparators AD7262

Open the catalog to page 1

Data Sheet

Open the catalog to page 2

Data Sheet SPECIFICATIONS AVCC = 4.75 V to 5.25 V, CA_CBVCC = CC_CDVCC = 2.7 V to 5.25 V, VDRIVE = 2.7 V to 5.25 V, fSAMPLE = 1 MSPS and fSCLK = 40 MHz for AD7262, fSAMPLE = 500 kSPS and fSCLK = 20 MHz for AD7262-5, VREF = 2.5 V internal/external; TA = −40°C to +105°C, unless otherwise noted. Table 1. Parameter DYNAMIC PERFORMANCE1 Signal-to-Noise Ratio (SNR)2 Signal-to-(Noise + Distortion) Ratio (SINAD)2 Total Harmonic Distortion (THD)2 Spurious-Free Dynamic Range (SFDR)2 Common-Mode Rejection Ratio (CMRR)3 Positive Full-Scale Error Match Zero Code Error2 Zero Code Error Match Negative...

Open the catalog to page 3

AD7262 Parameter LOGIC INPUTS Input High Voltage, VINH Input Low Voltage, VINL Input Current, IIN Input Capacitance, CIN3 LOGIC OUTPUTS Output High Voltage, VOH Output Low Voltage, VOL Floating State Leakage Current Floating State Output Capacitance3 Output Coding CONVERSION RATE Conversion Time Track-and-Hold Acquisition Time Throughput Rate COMPARATORS Input Offset Comparator A and Comparator B Comparator C and Comparator D Offset Voltage Drift Input Common-Mode Range3 Input Capacitance3 Input Impedance3 IDD Normal Mode (Static) 6 Comparator A and Comparator B Comparator C and Comparator...

Open the catalog to page 4

Data Sheet Parameter POWER REQUIREMENTS AVCC CA_CBVCC, CC_CDVCC VDRIVE IDD ADC Normal Mode (Static) ADC Normal Mode (Dynamic) Shutdown Mode Power Dissipation ADC Normal Mode (Static) ADC Normal Mode (Dynamic) Shutdown Mode Test Conditions/Comments Digital inputs = 0 V or VDRIVE AVCC = 5.25 V AVCC = 5.25 V AVCC = 5.25 V, ADCs and comparators powered down These specifications were determined without the use of the gain calibration feature. See the Terminology section. Samples tested during initial release to ensure compliance; they are not subject to production testing. 4 For PGA gain = 1; to...

Open the catalog to page 5

Data Sheet TIMING SPECIFICATIONS AVCC = 4.75 V to 5.25 V, CA_CBVCC = CC_CDVCC = 2.7 V to 5.25 V, VREF = 2.5 V internal/external; TA = TMIN to TMAX, unless otherwise noted. 1 Table 2. Parameter fSCLK Description AD7262 2 AD72622 AD7262-5 tSCLK = 1/fSCLK AD7262 AD7262-5 Minimum time between end of serial read/bus relinquish and next falling edge of CS CS to SCLK setup time Delay from 19th SCLK falling edge until DOUTA and DOUTB are three-state disabled Data access time after SCLK falling edge SCLK to data valid hold time SCLK high pulse width SCLK low pulse width CS rising edge to falling...

Open the catalog to page 6All Analog Devices catalogs and technical brochures

-

HMC722LP3E

8 Pages

-

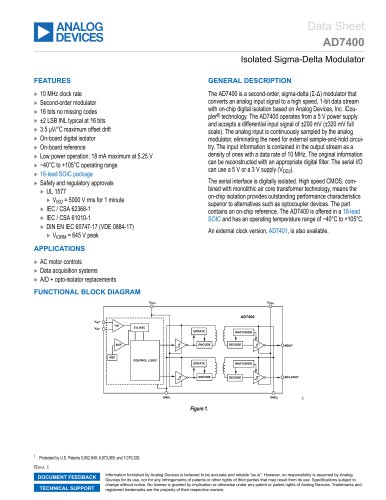

Isolated Sigma-Delta Modulator

17 Pages

-

HMC853 Data Sheet

10 Pages

-

AN-1084

8 Pages

-

AN-1091

2 Pages

-

AN_737

8 Pages

-

AN-0982

4 Pages

-

ADF7024

24 Pages

-

AD9915

48 Pages

-

AD9914

48 Pages

-

ADRF6612

59 Pages

-

ADRF6820

48 Pages

-

ADL5246

32 Pages

-

ADA4961

22 Pages

-

AN-1141

8 Pages

-

AN-698

36 Pages

-

Temperature Sensors

2 Pages

-

Reference Circuits

8 Pages

-

Precision ADCs

16 Pages

-

ADR02ACHIPS: ADR02ACHIPS

8 Pages

-

AD9364 RF Agile Transceiver

32 Pages

-

Digital Temperature Sensors

2 Pages

-

Digital to Analog Converter ICs

12 Pages

-

AD1836A: Multichannel 96 kHz Codec

24 Pages

Archived catalogs

-

Powering ADI Components

8 Pages

-

Zero-Drift Amplifiers

2 Pages