ウェブサイト:

TOPWAY LCD

ウェブサイト:

TOPWAY LCD

カタログの抜粋

SOLOMON SYSTECH SEMICONDUCTOR TECHNICAL DATA Advance Information 1215KB Embedded Display SRAM LCD Display Controller This document contains information on a new product. Specifications and information herein are subject to change without notice. http://www.solomon-systech.com SSD1963 Rev 1.1 P 1/93 Copyright © 2010 Solomon Systech Limited

カタログの1ページ目を開く

Appendix: IC Revision history of SSD1963 Specification Version 0.10 21-Nov-08 0.10 08-Dec-08 Change Items Changed status to Advance Information Update min/max rating of VDDD and VDDPLL in Table 11-1 Added tape and reel drawing of 128-pin LQFP package in Section 15.3 Revised Section 13.2 5. Added 12 bits for Table 7-1 Removed TTL interface Revised section 7.1.5 Change the title of section 7.2 Revised command description in section 8 Removed the command 0x0C and 0x3A Added figures in section 13.4 Revised figures in section 13.3 Revise Table 6-1 Update Table 7-1 Revised section 9.72 Solomon...

カタログの2ページ目を開く

Solomon Systech

カタログの3ページ目を開く

Solomon Systech

カタログの4ページ目を開く

Solomon Systech

カタログの5ページ目を開く

Solomon Systech

カタログの6ページ目を開く

Solomon Systec

カタログの7ページ目を開く

GENERAL DESCRIPTION SSD1963 is a display controller of 1215K byte frame buffer to support up to 864 x 480 x 24bit graphics content. It also equips parallel MCU interfaces in different bus width to receive graphics data and command from MCU. Its display interface supports common RAM-less LCD driver of color depth up to 24 bit-perpixel. Display feature − Built-in 1215K bytes frame buffer. Support up to 864 x 480 at 24bpp display − Support TFT 18/24-bit generic RGB interface panel − Support 8-bit serial RGB interface − Hardware rotation of 0, 90, 180, 270 degree − Hardware display mirroring −...

カタログの8ページ目を開く

BLOCK DIAGRAM Figure 4-1: SSD1963 Block Diagram Solomon Systech

カタログの9ページ目を開く

80 balls TFBGA Figure 5-1: Pinout Diagram –TFBGA (Topview) Solomon Systech Signal Name LDATA4 LDATA3 LDATA2 LDATA1 VSS VDDD R/W# (WR#) D[4] VDDPLL LDATA18 LDATA19 LDATA0 D[19] VSS VDDD E(RD#) D[3] CLK

カタログの10ページ目を開く

Figure 5-2 : Pinout Diagram – LQFP (Topview) Solomon Systech

カタログの11ページ目を開く

Signal Name VDDD VSS VSS VDDIO VSS VDDD D0 D1 D2 D3 D4 VDDIO VSS VDDD CLK VDDIO VSS VDDPLL VSSPLL VSS VDDD XTAL_IN VSS XTAL_OUT VDDD VSS VDDLCD LDATA23 LDATA22 LDATA21 LDATA20 VDDD Solomon Systech Signal Name VSS VDDLCD LDATA17 GPIO0 GPIO1 GPIO2 GPIO3 VDDD VSS VDDLCD LFRAME LLINE LSHIFT VDDD VSS VDDLCD LDEN TE PWM GAMAS0 GAMAS1 VDDLCD VSS VDDD VSS VDDLCD LDATA16 LDATA15 LDATA14 LDATA13 LDATA12 VDDD Signal Name VDDIO D17 D16 VDDIO VSS VDDD D15 D14 D13 D12 D11 VDDIO VSS VDDD D10 D9 D8 D7 D6 D5 VDDIO VSS VDDD R/W#(WR#) E(RD#) D/C# CS# VDDIO VSS VDDD RESET# CONF

カタログの12ページ目を開く

Key: I = Input O =Output IO = Bi-directional (input/output) P = Power pin Hi-Z = High impedance Table 6-1: MCU Interface Pin Mapping Pin Name Reference Type Voltage Level VDDIO VDDIO Description TTL clock input. This pin should be tied to VSS if TTL clock input is not used Crystal oscillator input. This pin should be tied to VSS if not used Crystal oscillator output. This pin should be floating if not used Chip select Data/Command select 6800 mode: E (enable signal) 8080 mode: RD# (read strobe signal) 6800 mode: R/W# 0: Write cycle 1: Read cycle 8080 mode: WR# (write strobe signal) Solomon...

カタログの13ページ目を開く

Table 6-2: LCD Interface Pin Mapping Pin Name LFRAME LLINE LSHIFT LDEN Reference Type Voltage Level O VDDLCD O VDDLCD O VDDLCD O VDDLCD VDDLCD VDDLCD Description Vertical sync (Frame pulse) Horizontal sync (Line pulse) Pixel clock (Pixel shift signal) Data valid These pins can be configured for display 36, 37, 38, 39 miscellaneous signals or as general purpose I/O. Default as input 52, 53 Gamma selection for panel 51 PWM output for backlight driver Table 6-3: Control Signal Pin Mapping Pin Name RESET# CONF Reference Type Voltage Level I VDDIO I Description Master synchronize reset MCU...

カタログの14ページ目を開く

Note (1) These pin mappings use signal names commonly used for each panel type, however signal names may differ between panel manufacturers. Solomon Systech

カタログの15ページ目を開く

FUNCTIONAL BLOCK DESCRIPTIONS The MCU interface connects the MCU and SSD1963 graphics controller. The MCU interface can be configured as 6800 mode and 8080 mode by the CONF pin. By pulling the CONF pin to VSSIO, the MCU interface will be configured as 6800 mode interface. If the CONF pin is connected to VDDIO, the MCU interface will be configure in 8080 mode. The 6800 mode MCU interface consist of CS#, D/C#, E, R/W#, D[23:0], and TE signals (Please refer to Table 6-1 for pin multiplexed with 8080 mode). This interface supports both fixed E and clock E scheme to define a read/write cycle. If...

カタログの16ページ目を開く

Table 7-1: Pixel Data Format Tearing Effect Signal (TE) The Tearing Effect Signal (TE) is a feedback signal from the LCD Controller to MCU. This signal reveals the display status of LCD controller. In the non-display period, the TE signal will go high. Therefore, this signal enables the MCU to send data by observing the non-display period to avoid tearing. Figure 7-1 shows how the TE signal helps to avoid tearing. If the MCU writing speed is slower than the display speed, the display data should be updated after the LCD controller start to scan the frame buffer. Then the LCD controller will...

カタログの17ページ目を開く

Figure 7-1: Relationship between Tearing Effect Signal and MCU Memory Writing In SSD1963, users can configure the TE signal to reflect the vertical non-display period only or reflect both vertical and horizontal non-display period. With the additional horizontal non-display period information, the MCU can control the refresh action in more accurately by counting the horizontal line scanned by the LCD controller. Usually, a fast MCU will not need horizontal non-display period. But a slow MCU will need it to ensure the frame buffer update process always lags behind the LCD controller. System...

カタログの18ページ目を開く

Figure 7-2: Clock Control Diagram set_pll bit 1 set_pll bit 0 EXTERNAL CRYSTAL Frame Buffer There are 1215K bytes built-in SRAM inside SSD1963 to use as frame buffer. When the frame buffer is written or read, the “address counter” will automatically increase by one or decrease by one depends on the frame buffer settings. Table 7-2: Frame Buffer Settings regarding to set_address_mode command 0x36 System Clock and Reset Manager The “System Clock and Reset Manager” distributes the reset signal and clock signal to the entire system. It controls the Clock Generator and contains clock gating...

カタログの19ページ目を開くTOPWAY LCDのすべてのカタログと技術パンフレット

-

10.1" TFT LCD Module

1 ページ

-

MONO Product

2 ページ

-

LMT050DNCFWU-NNA-2

15 ページ

-

LMT080TDGP01

16 ページ

-

HKT035BTB-1D

36 ページ

-

HMT050AMC-C

17 ページ

-

HMT043ATA-6C

31 ページ

-

TM035PDHG09

42 ページ

-

TM035PDHG03

31 ページ

-

TM028HDZP01

28 ページ

-

LM256160DCW-1

14 ページ

-

LM12896FCW-1

17 ページ

-

LM12832KCW

13 ページ

-

LM2088EFW-9

12 ページ

-

LM3122AGG-2

12 ページ

-

LM240160YCW

18 ページ

-

LM6093ACW

14 ページ

-

HMT104ATA-C

11 ページ

-

HMT101ATA-D

36 ページ

-

HKT080ATA-C

1 ページ

-

HMT080ATA

1 ページ

-

HKT070DTA-1C

11 ページ

-

HMT070DTA-D

1 ページ

-

HKT070DMC-2C

19 ページ

-

HMT070ETD-C

31 ページ

-

HMT070ETD-1D

34 ページ

-

HMT056ATA-C

1 ページ

-

HMT050CB-1C

31 ページ

-

HMT050DTA-D

1 ページ

-

HKT050ATA-C

1 ページ

-

HMT043ATA-7C

32 ページ

-

HMT043GTA-1D

37 ページ

-

HKT043BMC-2C

17 ページ

-

HMT043ATA-3C

11 ページ

-

HMT043BMC-C

1 ページ

-

HMT043ATA-4C

11 ページ

-

HKT043BMC-C

1 ページ

-

HKT043ATA-1C

12 ページ

-

HMT035ATA-D

13 ページ

-

HMT028ATB-C

12 ページ

-

HKT104ATA-C

31 ページ

-

HMT068BTA-C

33 ページ

-

HMT070ATA-1C

32 ページ

-

HMT080ATA-C

33 ページ

-

HMT090ATA-C

30 ページ

-

HMT101ATA-C

33 ページ

-

HMT050ATA-2C

31 ページ

-

HMT043ATA-2C

32 ページ

-

SGS-THOMSON ST7282

23 ページ

-

HMT035ATA-1C

1 ページ

-

Smart LCD introduction

14 ページ

-

TFT module in bezel

1 ページ

-

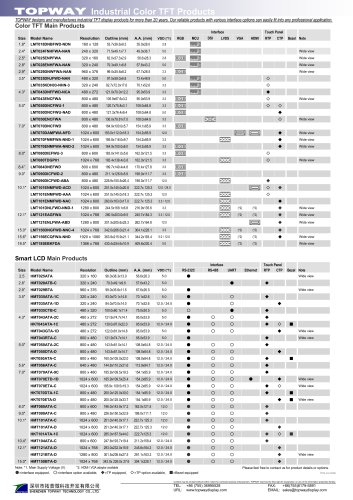

Topway TFT LCD

1 ページ

-

LM12864L Series

1 ページ

-

LM12864T Series

1 ページ

-

LM12864F Series

1 ページ

-

LM6060C Series

1 ページ

-

LM12864M Series

1 ページ

-

LM6029A Series

1 ページ

-

LM6059B Series

1 ページ

-

LM24048A Series

1 ページ

-

LM13232A Series

1 ページ

-

LM160160A Series

1 ページ

-

LMB402C Series

1 ページ

-

LMB242A Series

1 ページ

-

LMB204C Series

1 ページ

-

LM3121 Series

1 ページ

-

LMB404A Series

1 ページ

-

HMT043FC-1C

1 ページ

-

LM3123 Series

1 ページ

-

LMB204B Series

1 ページ

-

LMB202E Series

1 ページ

-

LMB202D Series

1 ページ

-

LMB164A Series

1 ページ

-

LMB162G Series

1 ページ

-

LMB162H Series

1 ページ

-

LMB162N Series

1 ページ

-

LMB162A Series

1 ページ

-

LMB0820D Series

1 ページ

-

LMB0820C Series

1 ページ

-

LMB0820A Series

1 ページ

-

LMB081N Series

1 ページ

-

LMB081A Series

1 ページ

-

LMB162X series

1 ページ

-

LMT104SDH01 Series

1 ページ

-

TFT LCD module

1 ページ

-

Without controller

1 ページ

-

Chinese fonts

1 ページ

-

Built-in controller

1 ページ

-

Character module

1 ページ