Website:

Analog Devices

Website:

Analog Devices

ADSP-CM402F/CM403F/CM407F/CM408F/CM409F: Mixed-Signal Control Processor with ARM Cortex-M4 and 16-bit ADCs

124Pages

Catalog excerpts

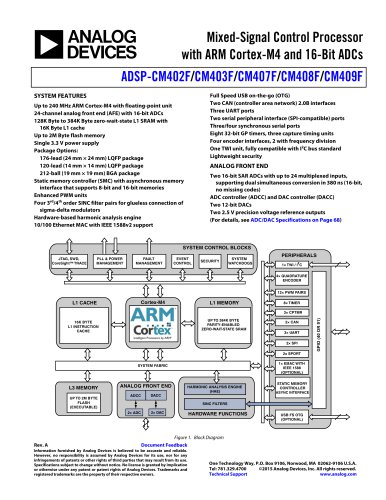

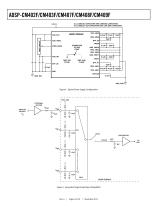

Mixed-Signal Control Processor with ARM Cortex-M4 and 16-Bit ADCs ADSP-CM402F/CM403F/CM407F/CM408F/CM409F SYSTEM FEATURES Full Speed USB on-the-go (OTG) Two CAN (controller area network) 2.0B interfaces Three UART ports Two serial peripheral interface (SPI-compatible) ports Three/four synchronous serial ports Eight 32-bit GP timers, three capture timing units Four encoder interfaces, 2 with frequency division One TWI unit, fully compatible with I2C bus standard Lightweight security Up to 240 MHz ARM Cortex-M4 with floating-point unit 24-channel analog front end (AFE) with 16-bit ADCs 128K Byte to 384K Byte zero-wait-state L1 SRAM with 16K Byte L1 cache Up to 2M Byte flash memory Single 3.3 V power supply Package Options: 176-lead (24 mm × 24 mm) LQFP package 120-lead (14 mm × 14 mm) LQFP package 212-ball (19 mm × 19 mm) BGA package Static memory controller (SMC) with asynchronous memory interface that supports 8-bit and 16-bit memories Enhanced PWM units Four 3rd/4th order SINC filter pairs for glueless connection of sigma-delta modulators Hardware-based harmonic analysis engine 10/100 Ethernet MAC with IEEE 1588v2 support ANALOG FRONT END Two 16-bit SAR ADCs with up to 24 multiplexed inputs, supporting dual simultaneous conversion in 380 ns (16-bit, no missing codes) ADC controller (ADCC) and DAC controller (DACC) Two 12-bit DACs Two 2.5 V precision voltage reference outputs (For details, see ADC/DAC Specifications on Page 68) SYSTEM CONTROL BLOCKS JTAG, SWD, CoreSight™ TRACE FAULT MANAGEMENT EVENT CONTROL SYSTEM WATCHDOGS 4× QUADRATURE ENCODER 12× PWM PAIRS 16K BYTE L1 INSTRUCTION CACHE 3× CPTMR UP TO 384K BYTE PARITY-ENABLED ZERO-WAIT-STATE SRAM 2x SPORT 1× EMAC WITH IEEE 1588 (OPTIONAL) SYSTEM FABRIC L3 MEMORY UP TO 2M BYTE FLASH (EXECUTABLE) ANALOG FRONT END ADCC STATIC MEMORY CONTROLLER ASYNC INTERFACE HARMONIC ANALYSIS ENGINE (HAE) HARDWARE FUNCTIONS Figure 1. Block Diagram Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106 U.S.A. Tel: 781.329.4700 ©2015 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

Open the catalog to page 1

ADSP-CM402F/CM403F/CM407F/CM408F/CM409F GENERAL DESCRIPTION Each ADSP-CM40xF family member contains the following modules. The ADSP-CM40xF family of mixed-signal control processors is based on the ARM® Cortex-M4TM processor core with floatingpoint unit operating at frequencies up to 240 MHz and integrating up to 384 kB of SRAM memory, 2 MB of flash memory, accelerators and peripherals optimized for motor control and photo-voltaic (PV) inverter control and an analog module consisting of two 16-bit SAR ADCs and two 12-bit DACs. The ADSP-CM40xF family operates from a single voltage supply...

Open the catalog to page 3

ADSP-CM402F/CM403F/CM407F/CM408F/CM409F ANALOG FRONT END The mixed-signal controllers contain two ADCs and two DACs. Control of these data converters is simplified by a powerful onchip analog-to-digital conversion controller (ADCC) and a digital-to-analog conversion controller (DACC). The ADCC and DACC are integrated seamlessly into the software programming model, and they efficiently manage the configuration and realtime operation of the ADCs and DACs. simultaneously or at different times and may be operated in asynchronous or synchronous modes. The best performance can be achieved in...

Open the catalog to page 4

ADCC CONTROL SRAM MEMORY DATA ADC/DAC LOCAL CONTROLLER DAC0 VREF0 VREF1 REFCAP NOTE: DAC0 AND DAC1 CAN BE MUX SELECTED THROUGH AN INTERNAL PATH WITHIN THE CHIP. SEE THE HARDWARE REFERENCE MANUAL FOR PROGRAMMING DETAIL. Figure 3. ADSP-CM407F/ADSP-CM408F Analog Subsystem Block Diagram Considerations for Best Converter Performance As with any high performance analog/digital circuit, to achieve best performance, good circuit design and board layout practices should be followed. The power supply and its noise bypass (decoupling), ground return paths and pin connections, and analog/digital...

Open the catalog to page 5

ADSP-CM402F/CM403F/CM407F/CM408F/CM409F ALL LABELED CAPACITORS ARE CERAMIC CAPACITORS. ALL LABELED 10μF CAPACITORS ARE LOW ESR CAPACITORS. VREG CIRCUIT VDD_INT GND_DIG PLANE GND_ANA PLANE Figure 4. Typical Power Supply Configuration VDD_ANA EXTERNAL BUFFER ANALOG SOURCE HOLD PRE-BUFFER TRACK Figure 5. Equivalent Single-Ended Input (Simplified)

Open the catalog to page 6

Microarchitecture • 3-stage pipeline with branch speculation The ARM Cortex-M4, core shown in Figure 6, is a 32-bit reduced instruction set computer (RISC). It uses 32-bit buses for instruction and data. The length of the data can be 8 bits, 16 bits, or 32 bits. The length of the instruction word is 16 or 32 bits. The controller has the following features. • Low-latency interrupt processing with tail chaining Configurable For Ultra Low Power • Deep sleep mode, dynamic power management • Programmable clock generator unit EmbeddedICETM provides integrated on-chip support for the core. The...

Open the catalog to page 7

• GPIO interrupt mask registers—Allow each individual GPIO pin to function as an interrupt to the processor. GPIO pins defined as inputs can be configured to generate hardware interrupts, while output pins can be triggered by software interrupts. The processor contains 17 independent and concurrently operating peripheral DMA channels plus two MDMA streams. DDE Channel 0 to Channel 16 are for peripherals and Channel 17 to Channel 20 are for MDMA. • GPIO interrupt sensitivity registers—Specify whether individual pins are level- or edge-sensitive and specify—if edge-sensitive—whether just the...

Open the catalog to page 8All Analog Devices catalogs and technical brochures

-

Powering ADI Components

8 Pages

-

HMC722LP3E

10 Pages

-

HMC853 Data Sheet

10 Pages

-

AN-1084

8 Pages

-

AN-1091

2 Pages

-

AN_737

8 Pages

-

AN-0982

4 Pages

-

ADF7024

24 Pages

-

AD9915

48 Pages

-

AD9914

48 Pages

-

ADRF6612

59 Pages

-

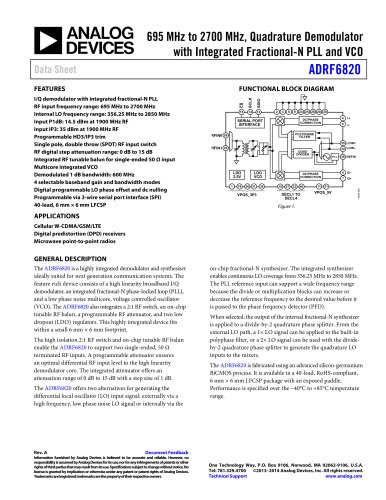

ADRF6820

48 Pages

-

ADL5246

32 Pages

-

ADA4961

22 Pages

-

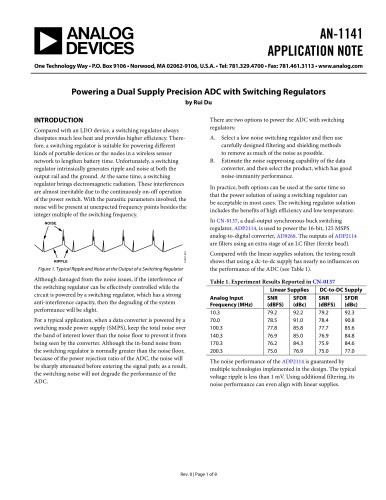

AN-1141

8 Pages

-

AN-698

36 Pages

-

Temperature Sensors

2 Pages

-

Reference Circuits

8 Pages

-

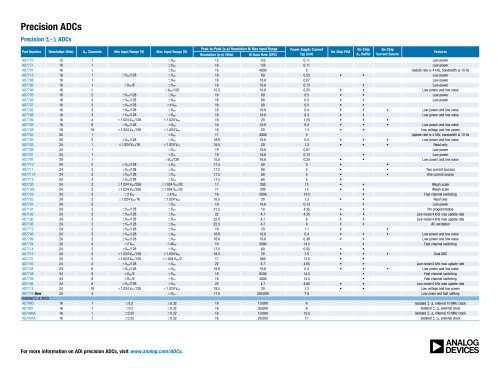

Precision ADCs

16 Pages

-

ADR02ACHIPS: ADR02ACHIPS

8 Pages

-

AD9364 RF Agile Transceiver

32 Pages

-

Digital Temperature Sensors

2 Pages

-

Digital to Analog Converter ICs

12 Pages

-

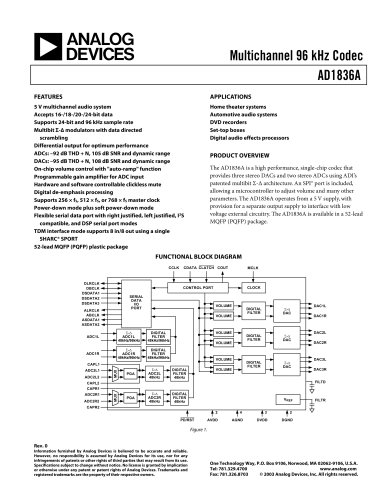

AD1836A: Multichannel 96 kHz Codec

24 Pages

-

Zero-Drift Amplifiers

2 Pages